verilog 开源工具链配置笔记

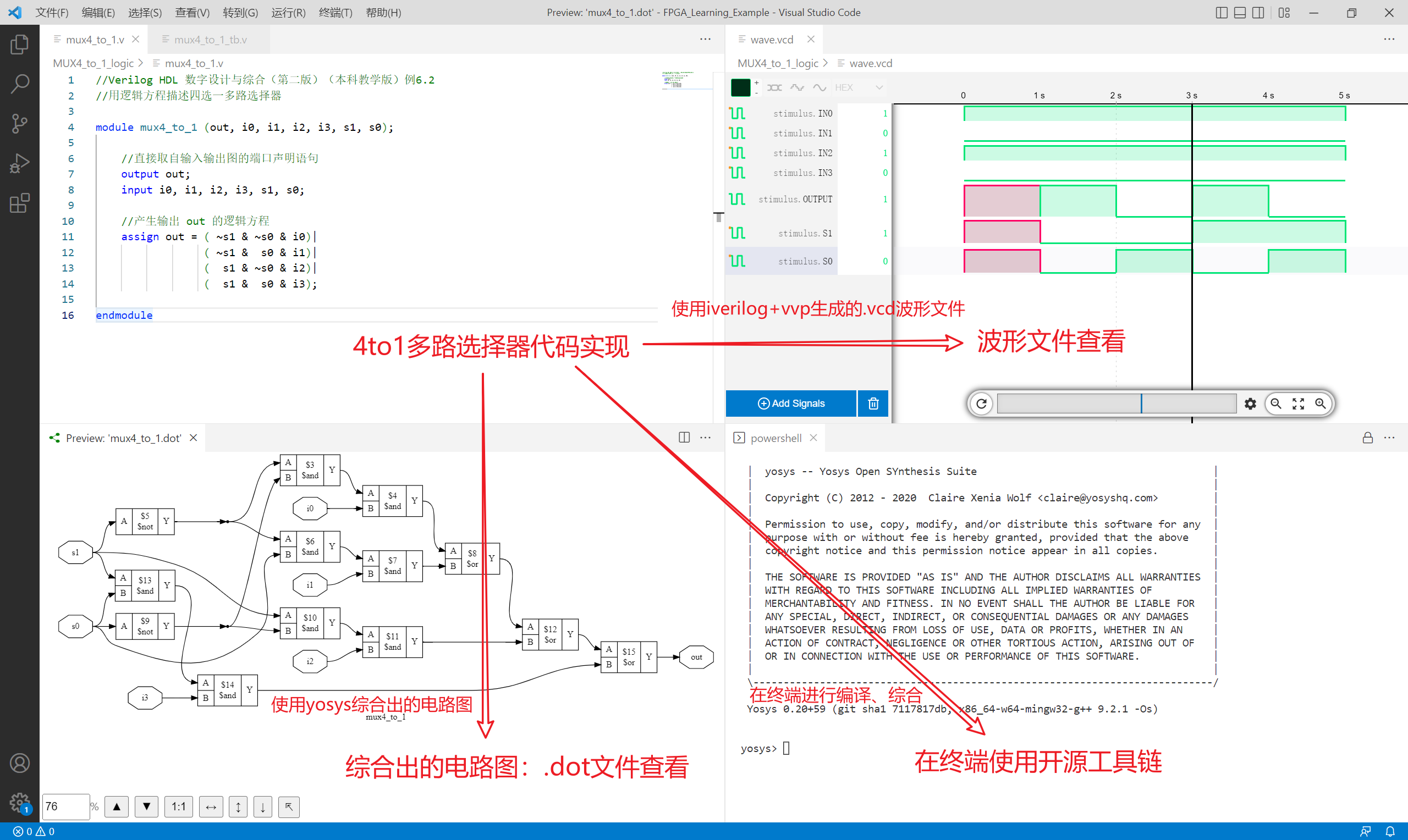

效果展示

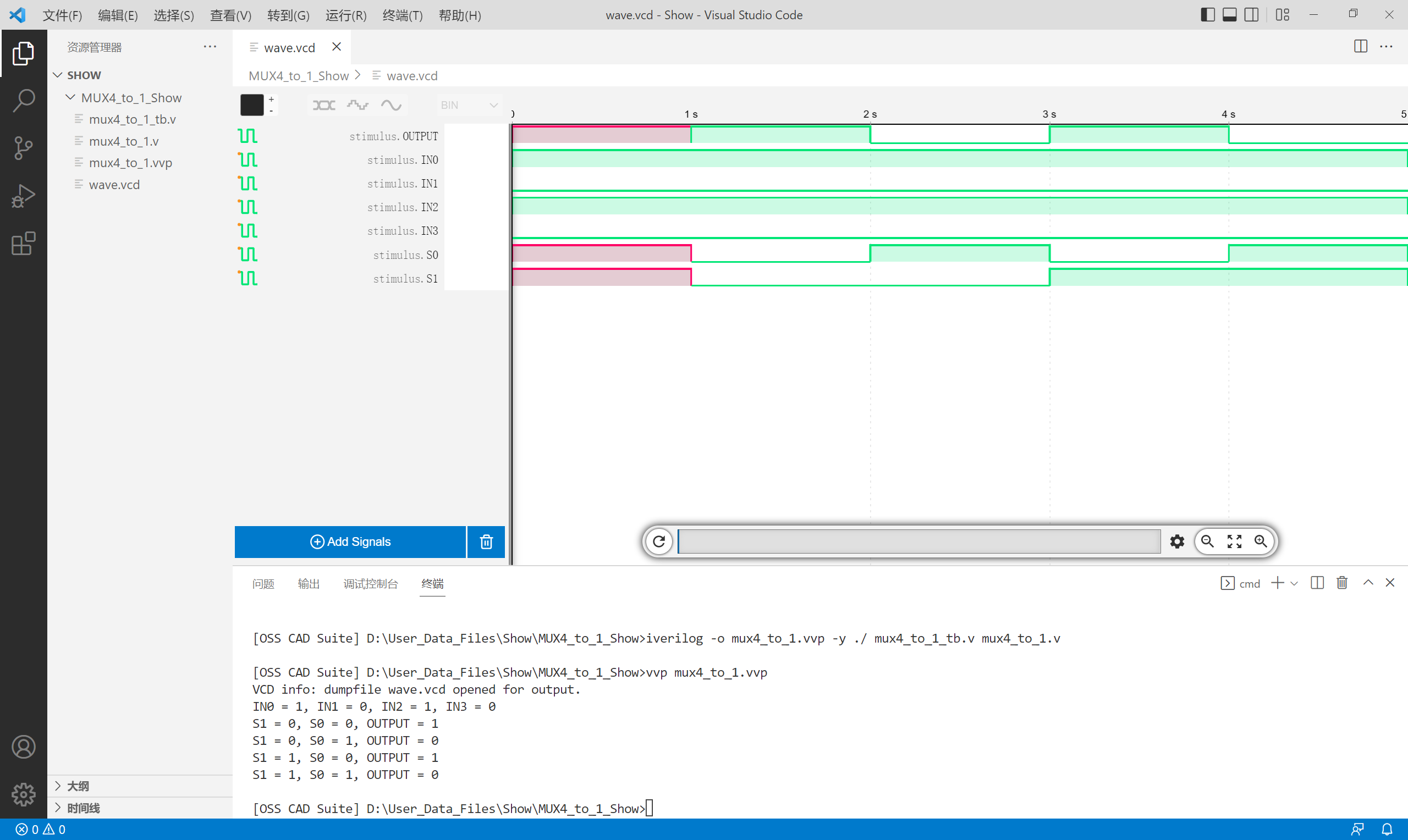

本文配置的最终效果展示如下:

Win11+VScode+oss-cad

工具介绍及安装

首先介绍一下 VScode。VSCode(全称:Visual Studio Code)是一款由微软开发且跨平台的免费源代码编辑器。该软件支持语法高亮、代码自动补全等功能。VScode 的强大之处在于用户可以通过内置的扩展程序商店安装扩展以拓展软件功能。你可以在 VScode 官网 下载并安装 VScode,安装方法非常简单,这里不再进行说明。

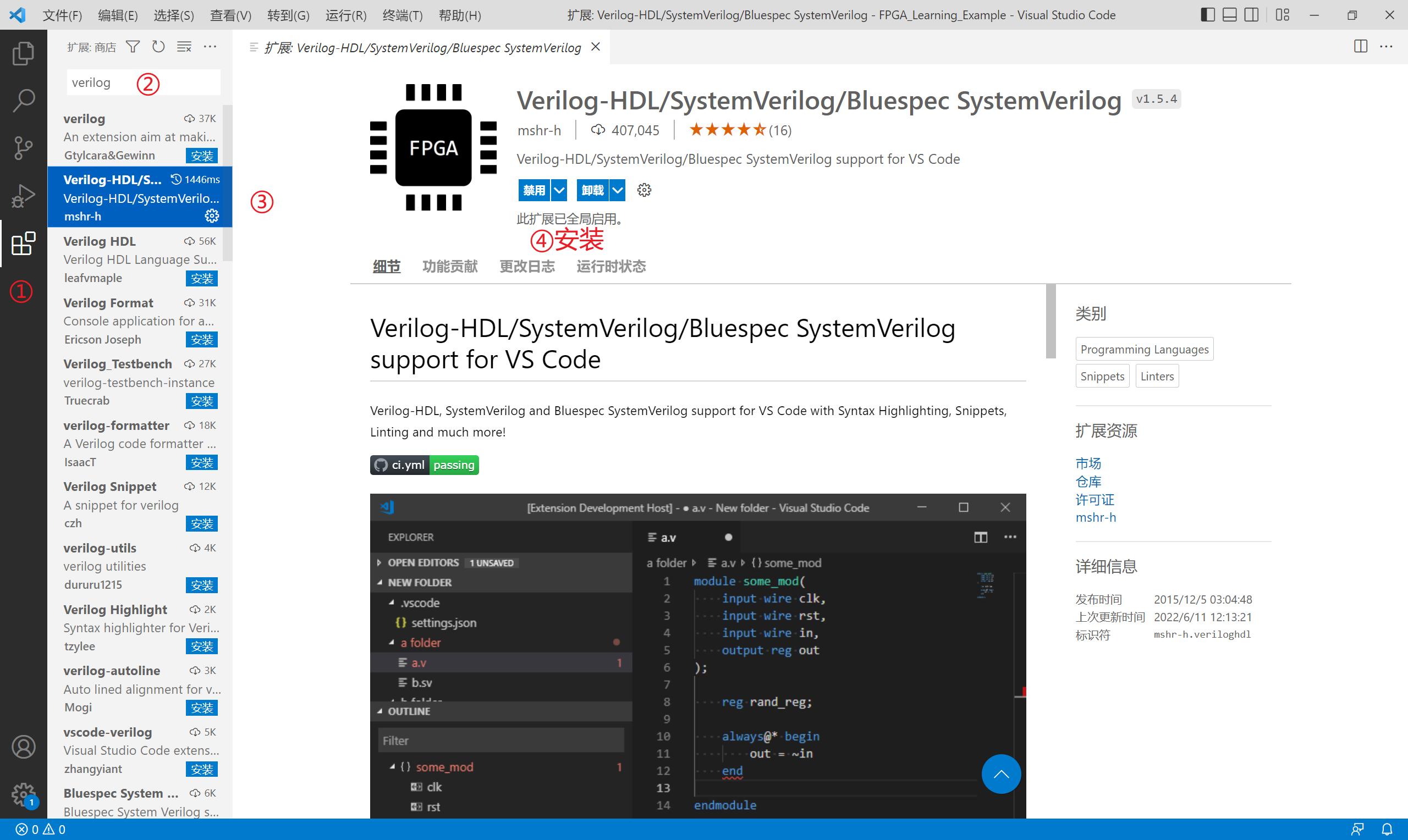

在 verilog 开发中,我们可以通过添加 "Verilog-HDL/SystemVerilog/Bluespec SystemVerilog support for VS Code" 插件实现 verilog 代码高亮和代码自动补全等功能。你可以直接在 VScode 的扩展中搜索并一键安装这个插件:

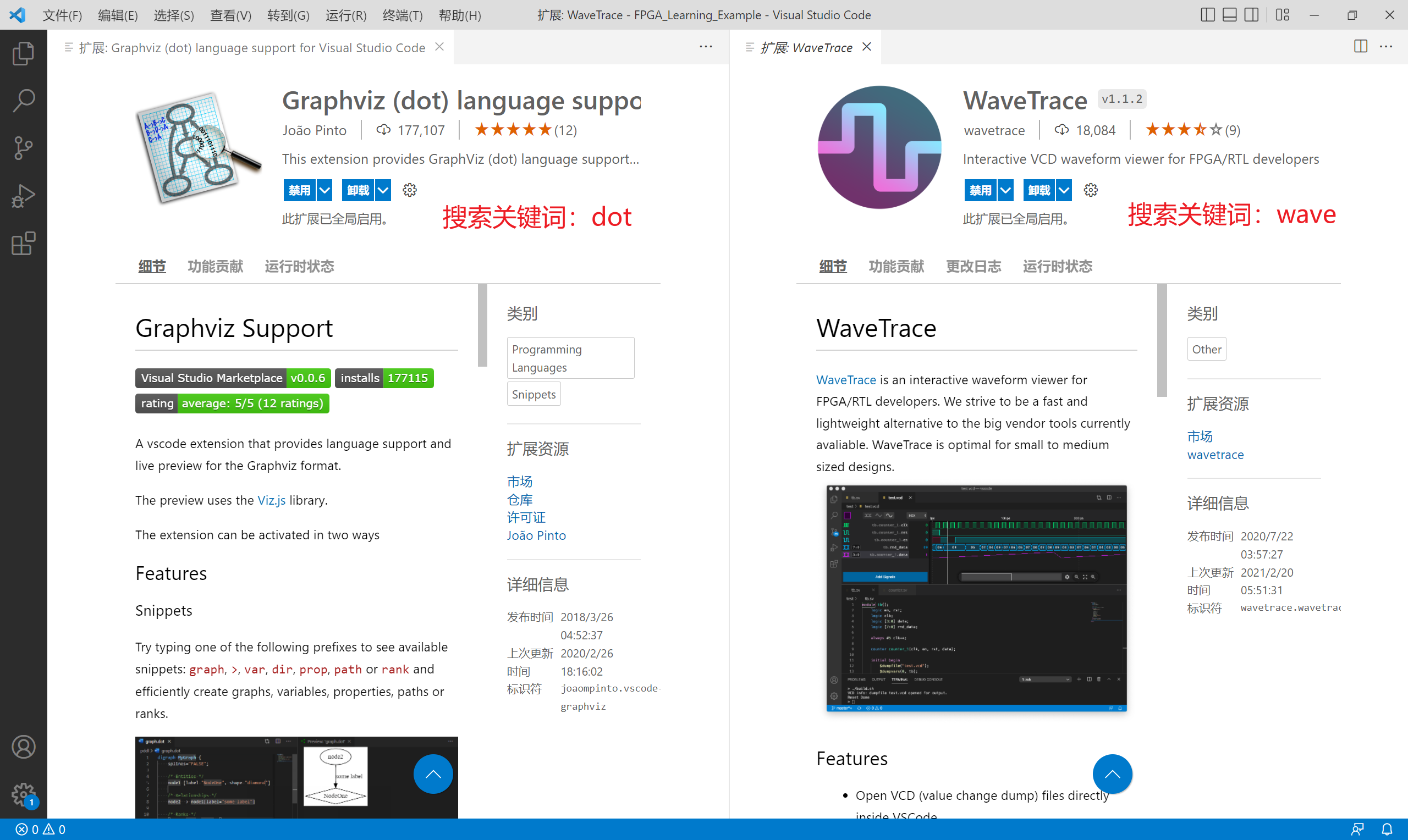

通过类似的方式,搜索并安装下面两个插件:

左边的插件可以帮助你查看综合出的 .dot 格式的电路图文件,右边的插件可以帮你根据 .vcd 文件生成波形图:

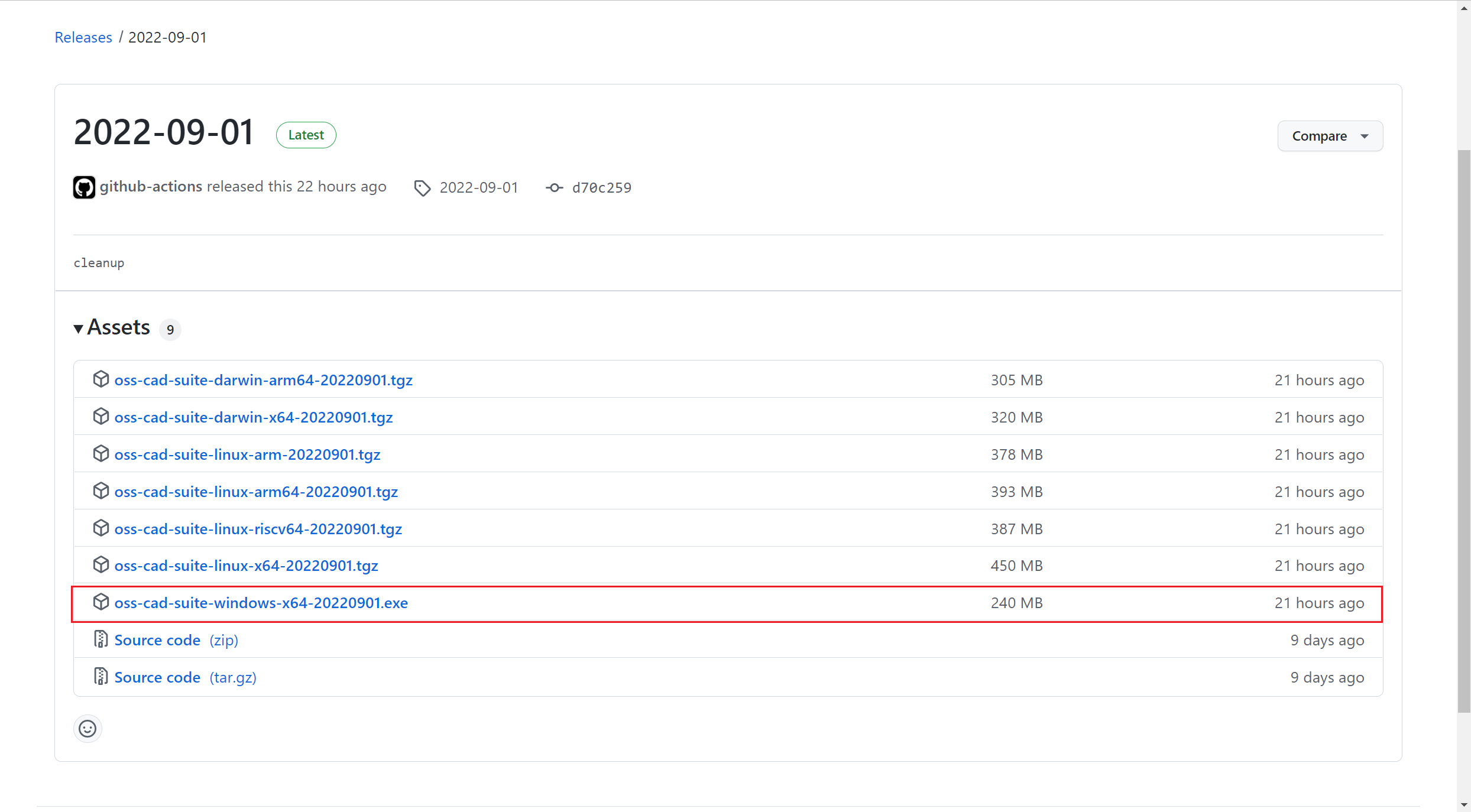

上面展示的 verilog 代码的编译和综合过程主要使用到了两个工具:iVerilog 和 Yosys。这两个工具,包括也是非常常用的波形查看工具 GTKwave 都被集成在了一个开源工具组件 OSS CAD Suite 中。OSS CAD 套件中还有很多用于数字逻辑设计的开源软件的二进制软件发行版。你可以在这个 GitHub 页面 中进行查看。

如果想要安装和使用 OSS CAD Suite ,我们可以直接在 这个界面 下载 .exe 文件:

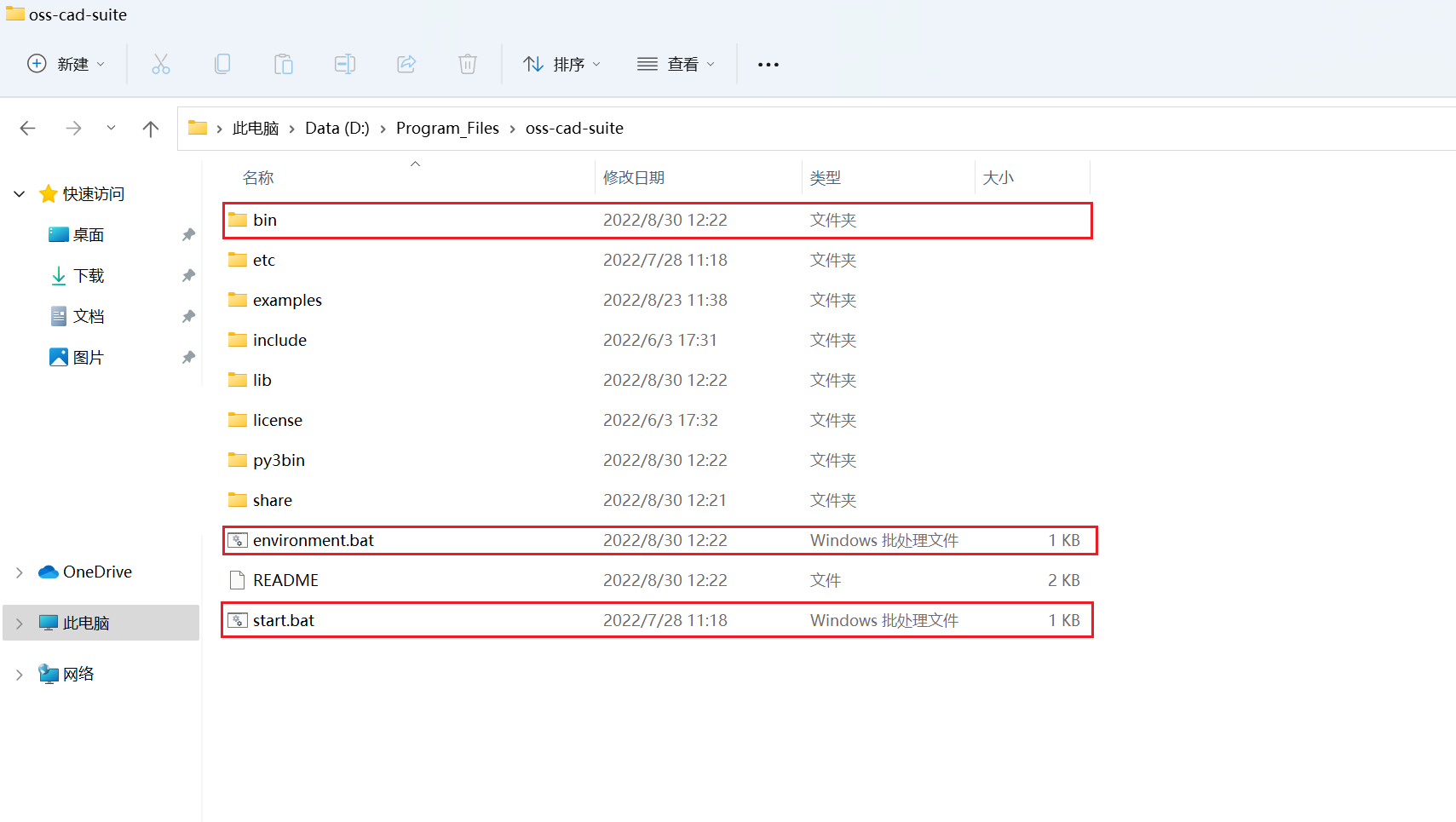

下载完成后直接运行这个 .exe 文件,即可获得这样一个文件夹:

我将这个 OSS CAD Suite 放在了我自己在 D盘 创建的 Program_Files 文件夹。在这个目录下,我们要重点关注第一个 bin 文件夹和最后标红的两个 .bat 文件。第一个 bin 文件夹里面是 OSS CAD Suite 介绍中所说的,用于数字逻辑设计的开源软件的二进制软件发行版。你可以从这个文件夹中找到包括 iVerilog、GTKwave 和 Yosys。

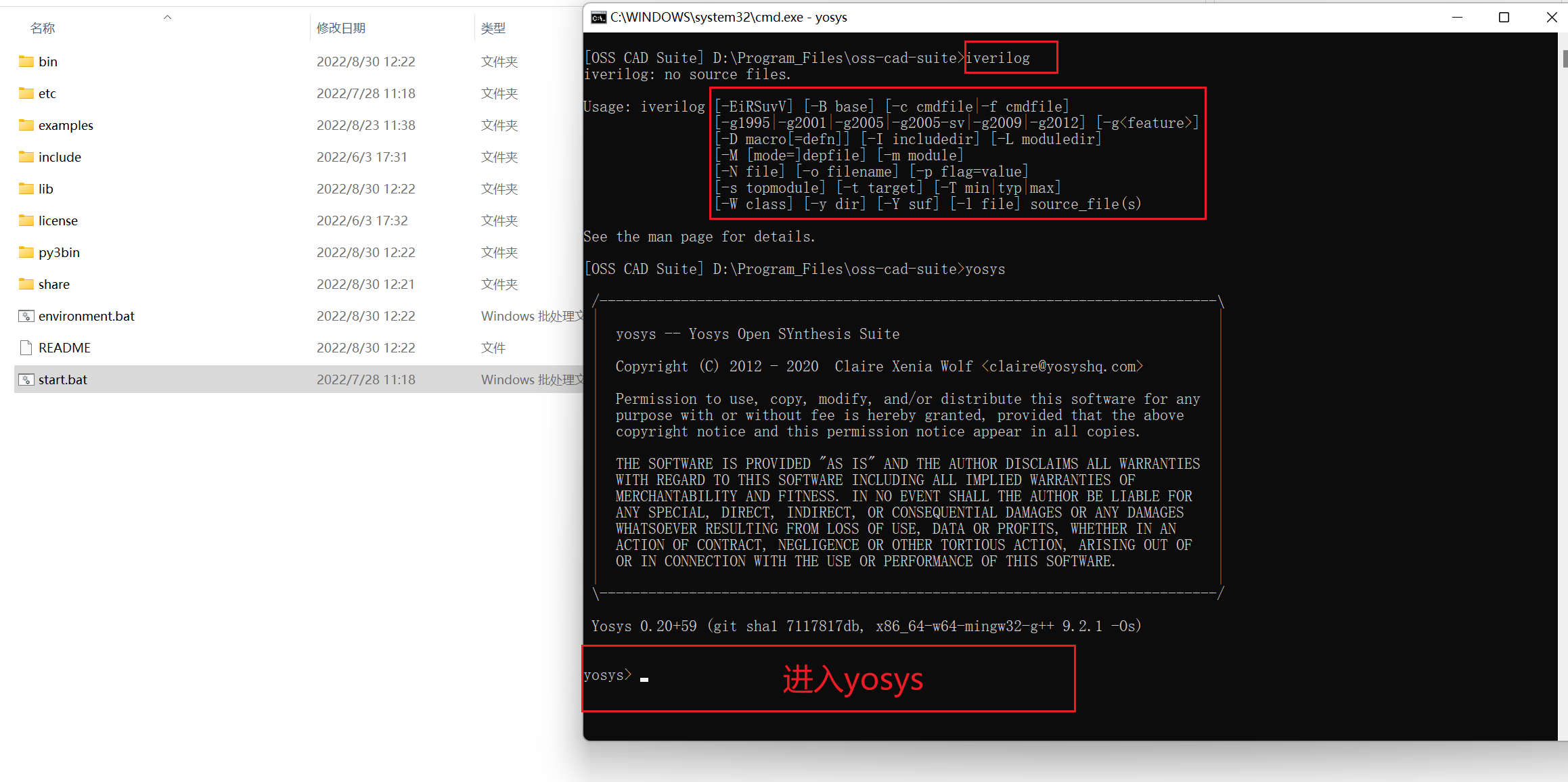

那么如何使用这些组件呢? OSS CAD Suite 提供了两种方法,一种是直接点击 start.bat 文件,然后使用命令的方式进行操作:

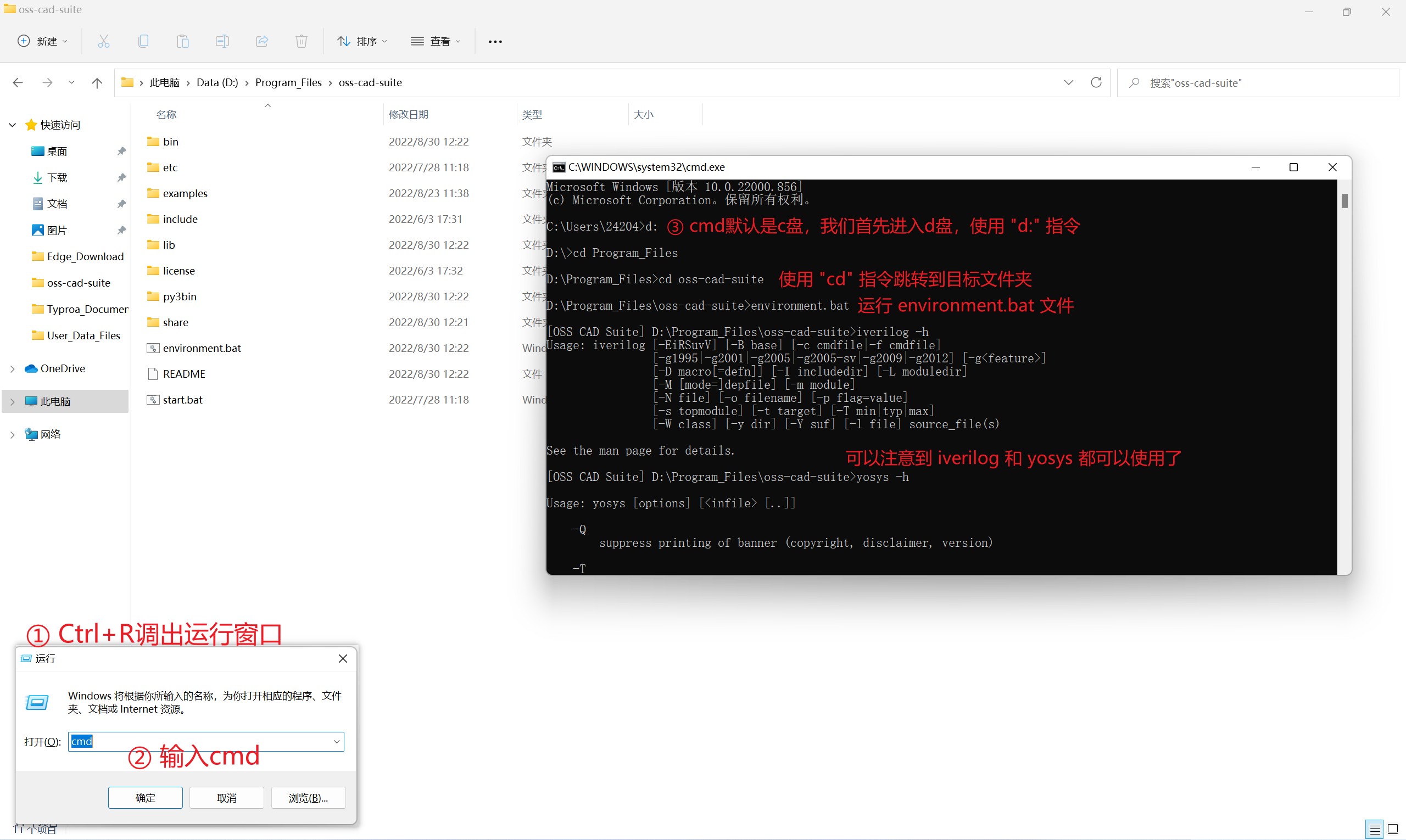

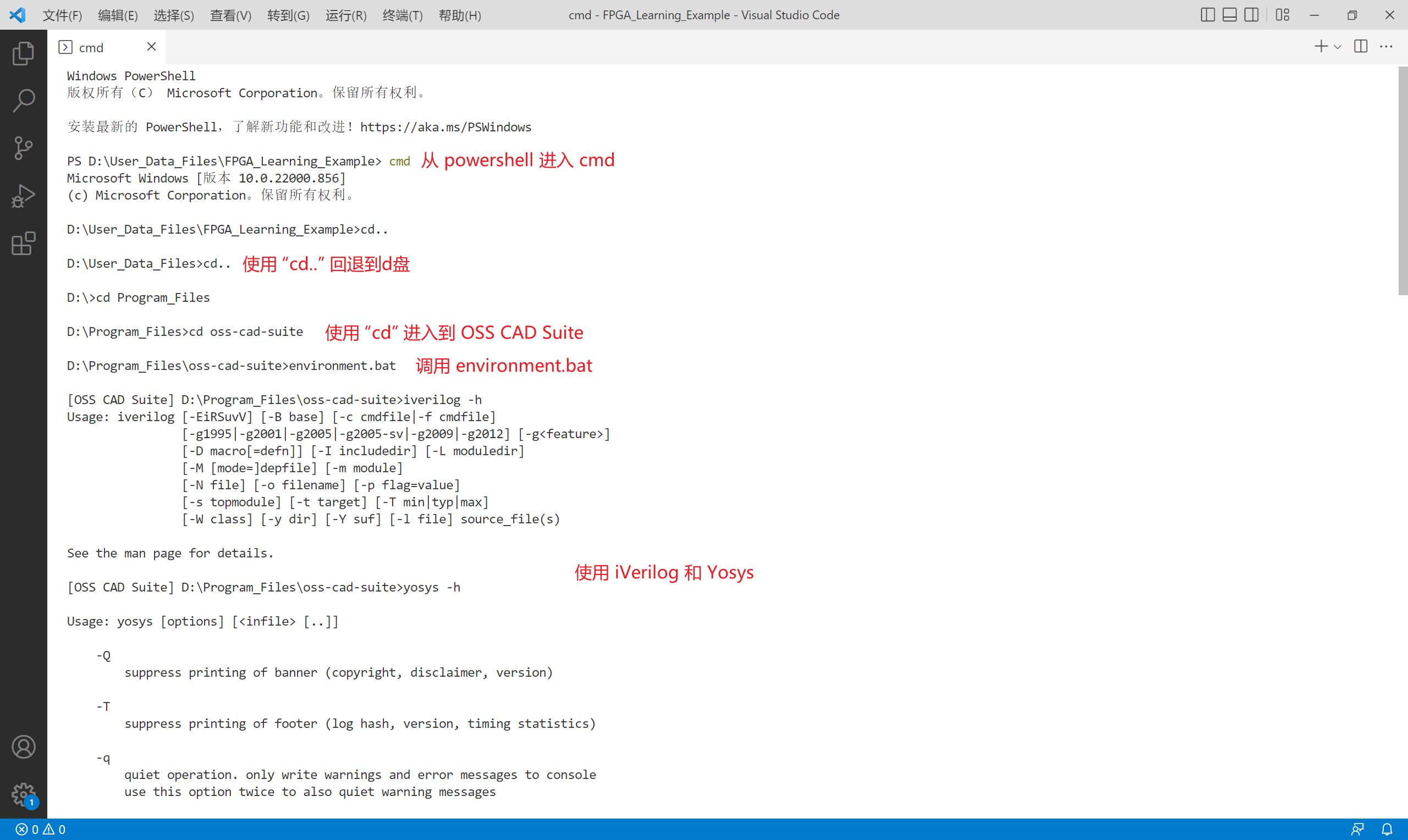

第二种方案是通过命令行工具,在 cmd 中调用 environment.bat 来使用该工具:

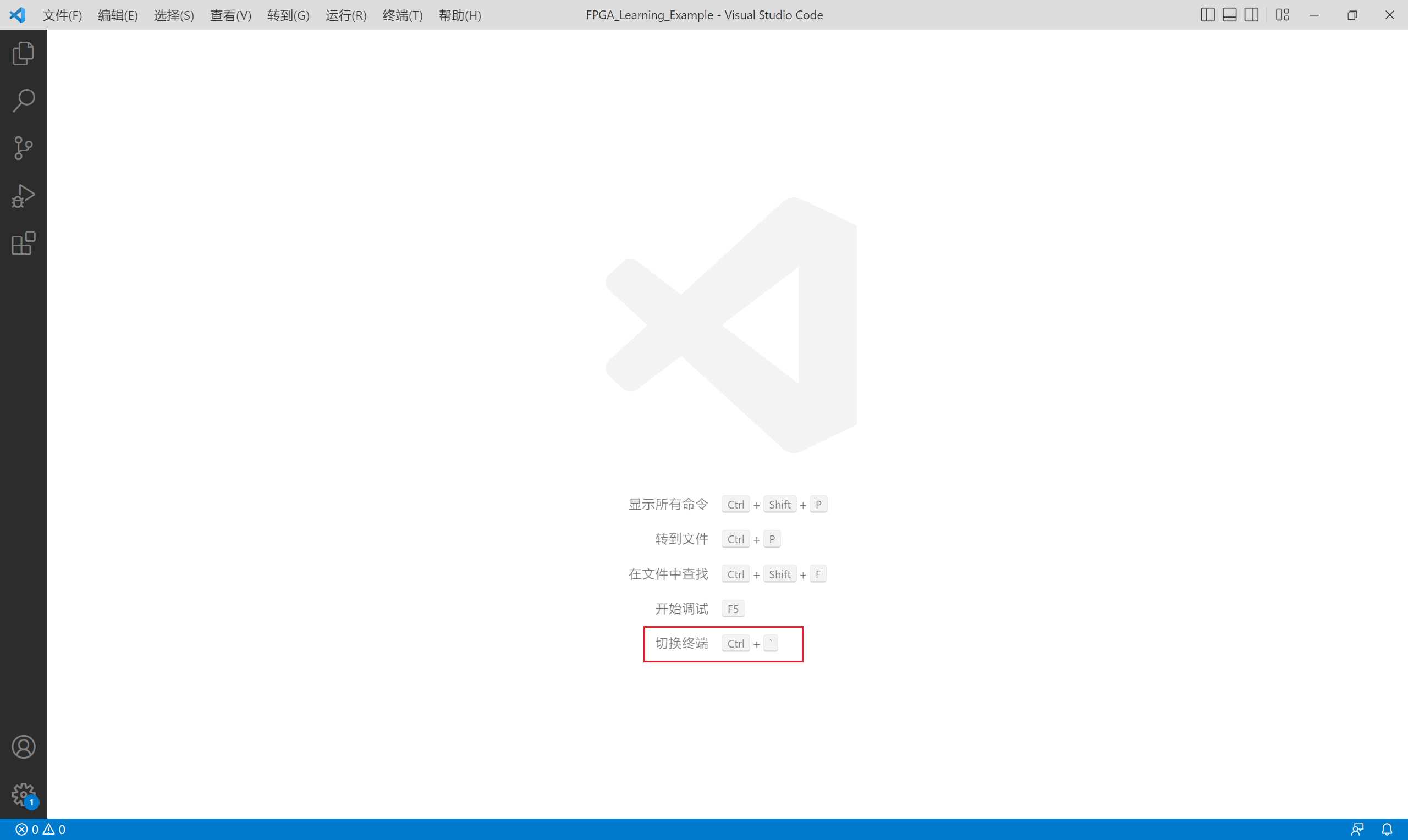

但是,之前我们的操作都是在 VScode 上进行的,所以我们希望也把 OSS CAD Suite 的使用放在 VScode 内进行,有没有办法呢?我的解决方案是使用第二种方法调用 OSS CAD Suite ,只要使用 VScode 内置的 cmd (终端)来实现调用 environment.bat 即可。操作如下:

首先如下图提示的,我们使用快捷键调出终端

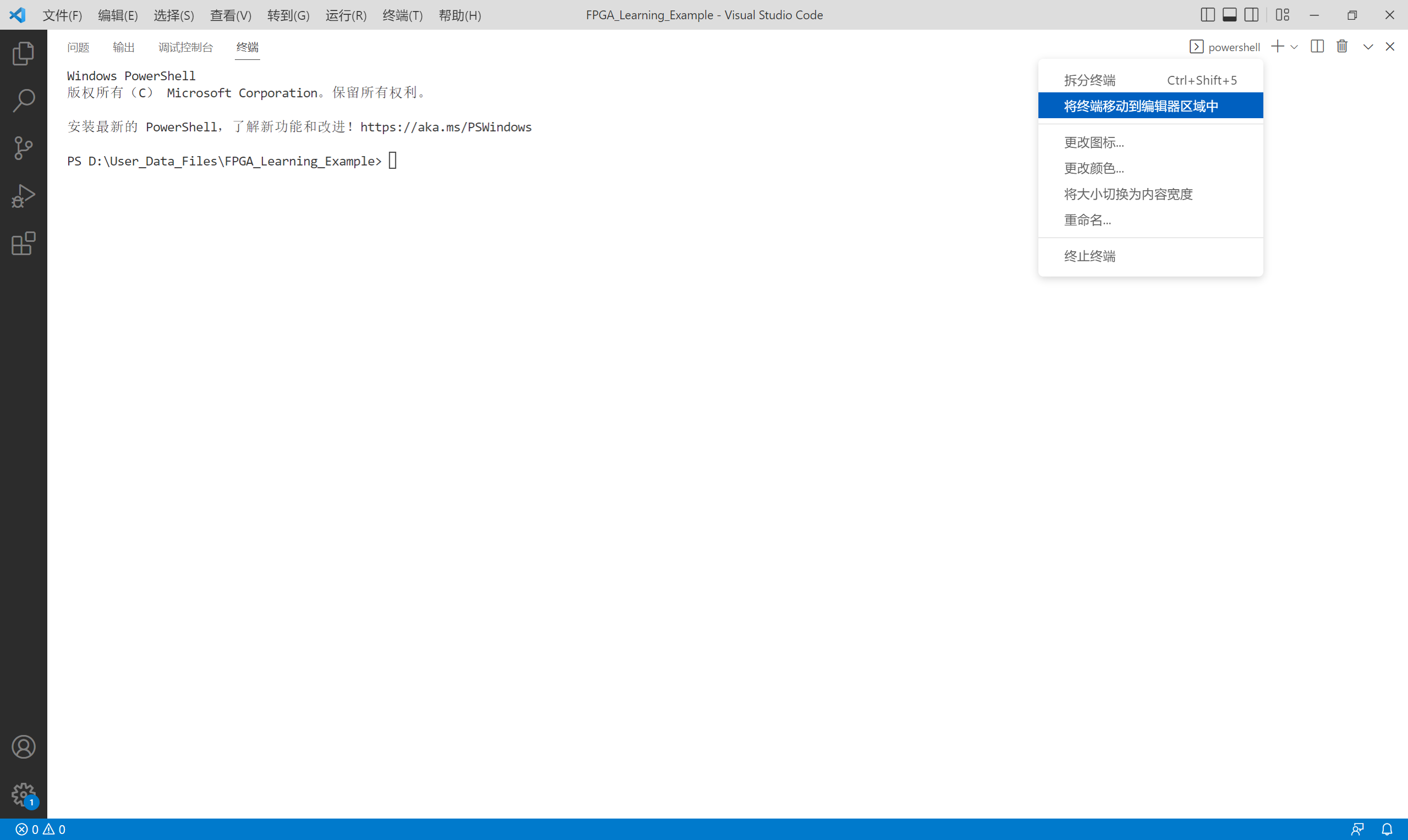

我们可以将终端移动到编辑器区域:

然后我们注意到这个终端不是 cmd,而是 powershell,两者的区别读者可以自己去查一下,这里我们还是使用 cmd 来演示:注意在 cmd 中可以使用 tab 键进行补全。

到此为止我们已经进行了全部内容的安装。下面我们使用一个 4 选 1 多路选择器代码进行演示:

使用方法

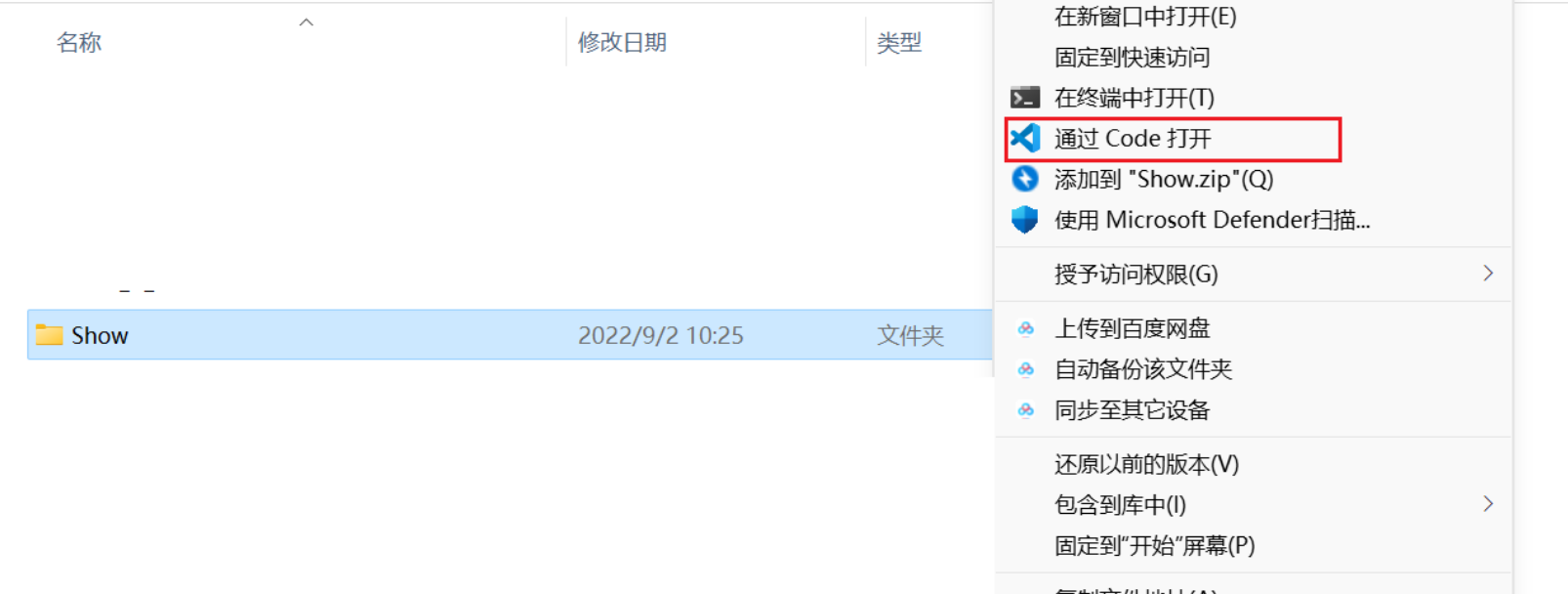

首先新建一个文件夹,然后选择使用 VScode 打开:

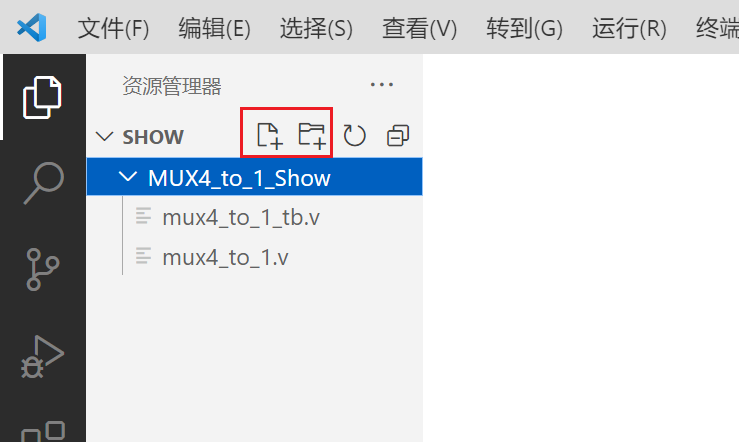

然后建立如下目录结构:红框内的第一个图标是新建文件,第二个是新建文件夹

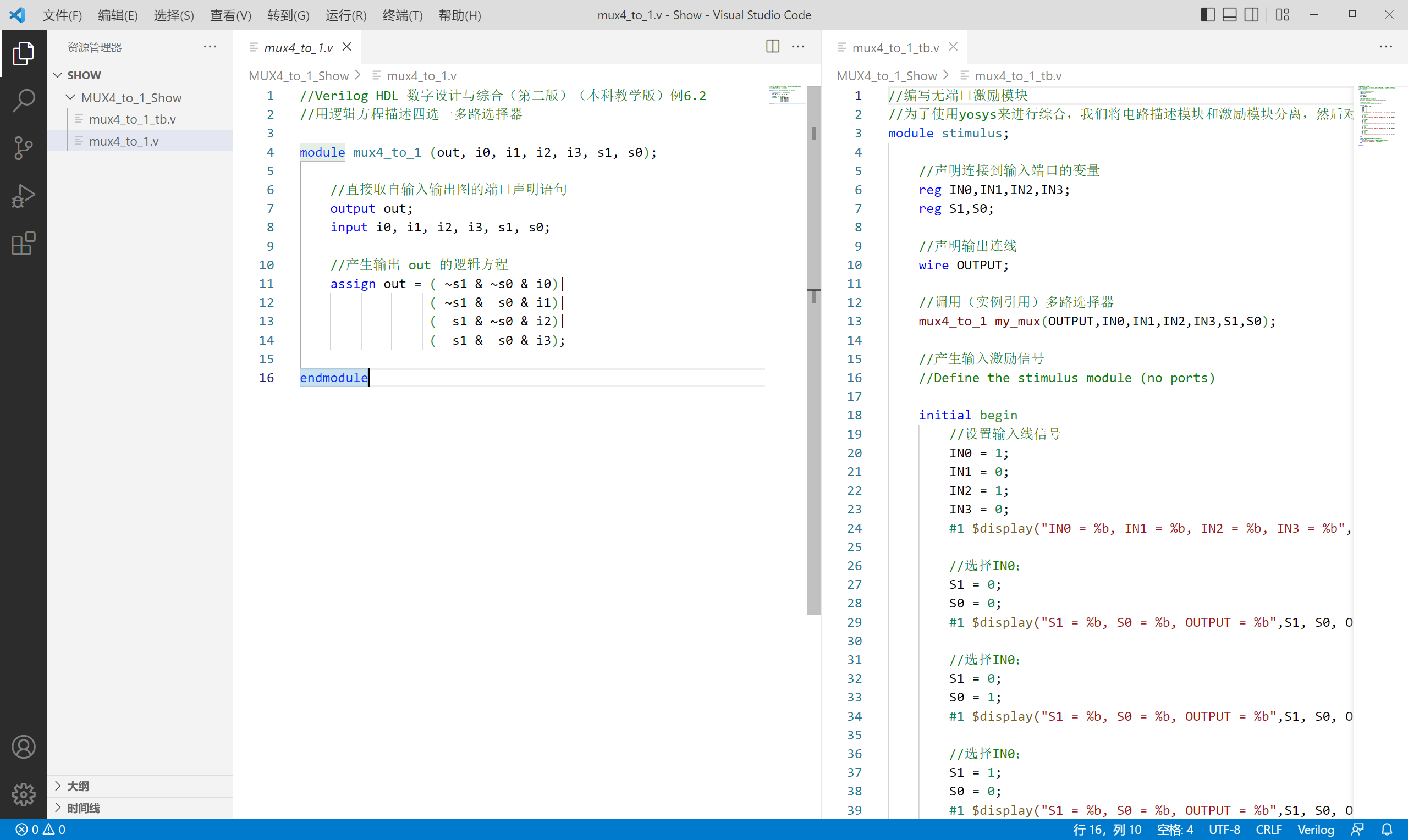

输入代码:

附上代码:

1 | //Verilog HDL 数字设计与综合(第二版)(本科教学版)例6.2 |

1 | //编写无端口激励模块 |

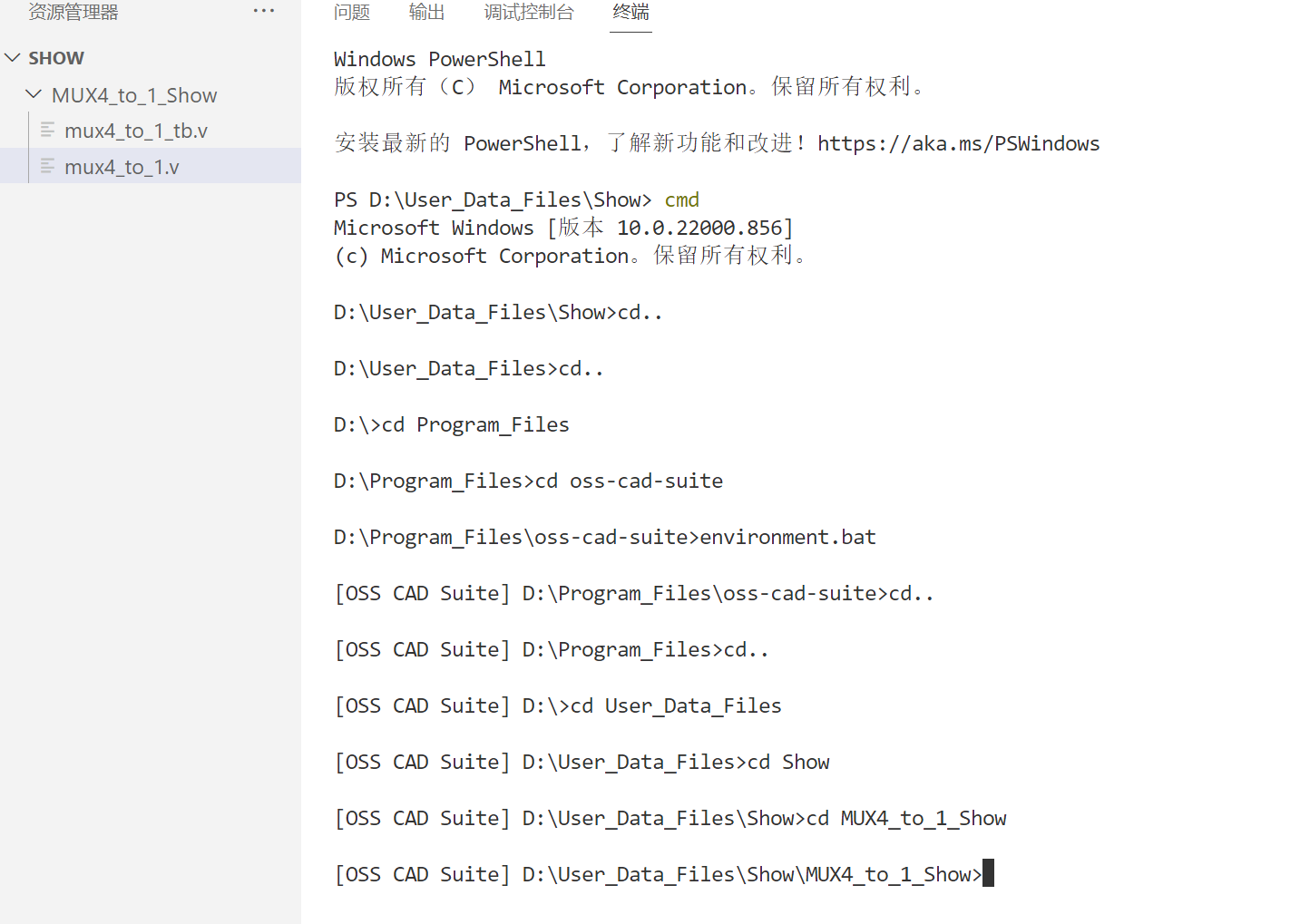

然后保存文件,打开终端,先进入 oss-cad-suite 文件夹打开 environment.bat 然后再回到 verilog 文件目录下对目标文件进行操作

然后进行编译等一系列操作:

1 | iverilog -o mux4_to_1.vvp -y ./ mux4_to_1_tb.v mux4_to_1.v |

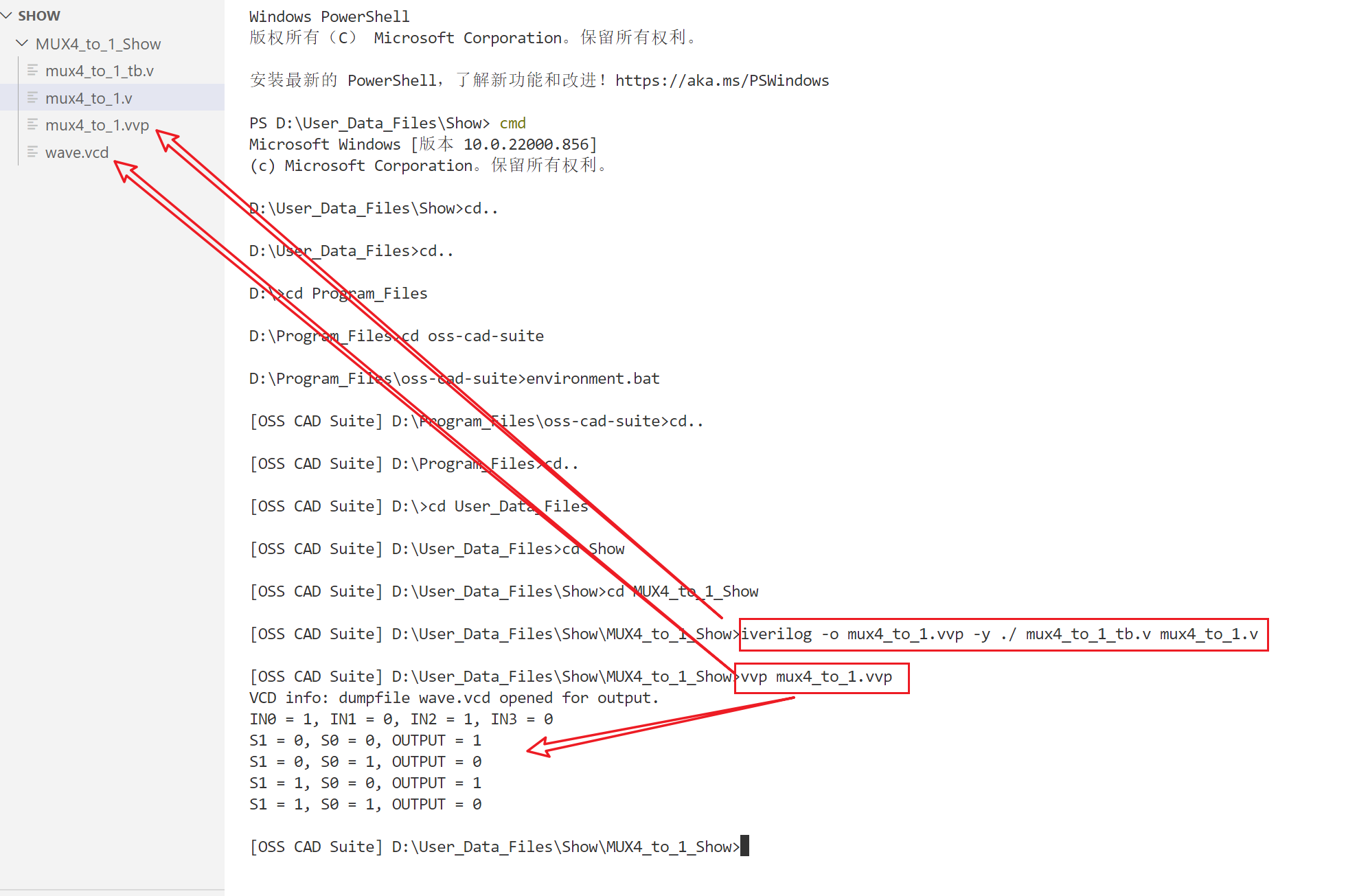

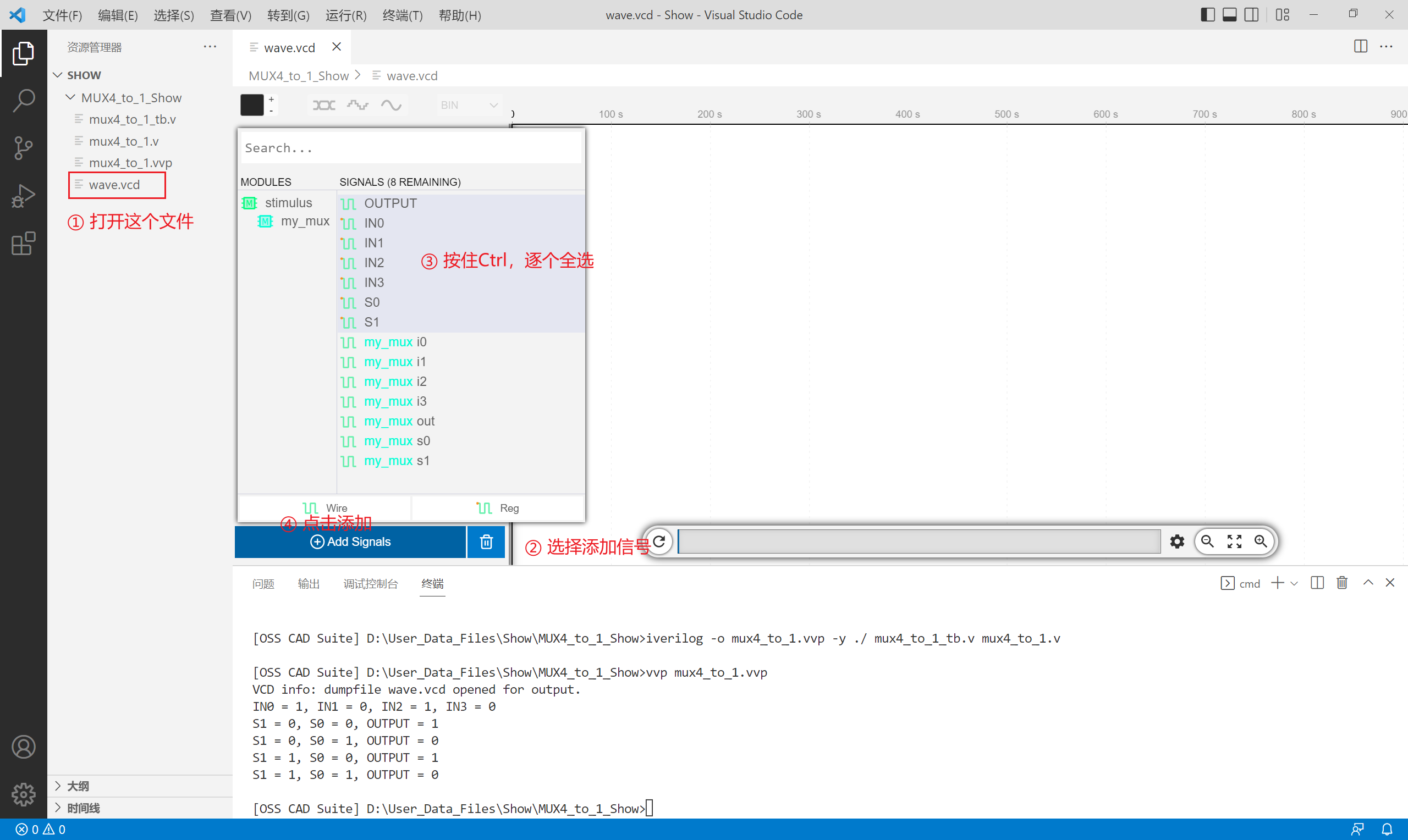

然后在终端可以看到 $display() 的内容,然后我们查看 .vcd

文件:

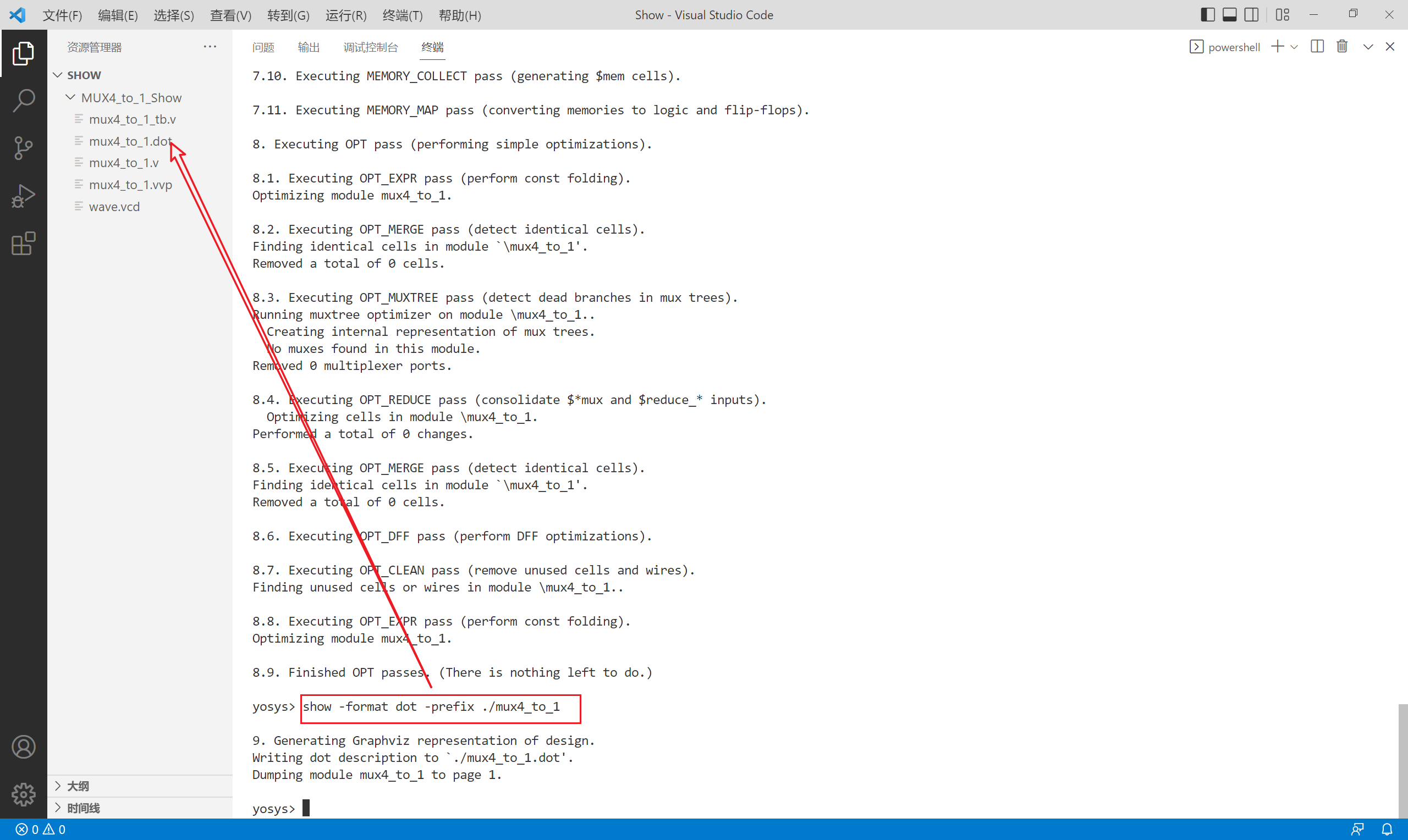

接下来我们进行综合:

首先进入 yosys,然后读入文件,处理文件,最后导出 .dot 格式

过程如下:

1 | read_verilog mux4_to_1.v |

得到结果:

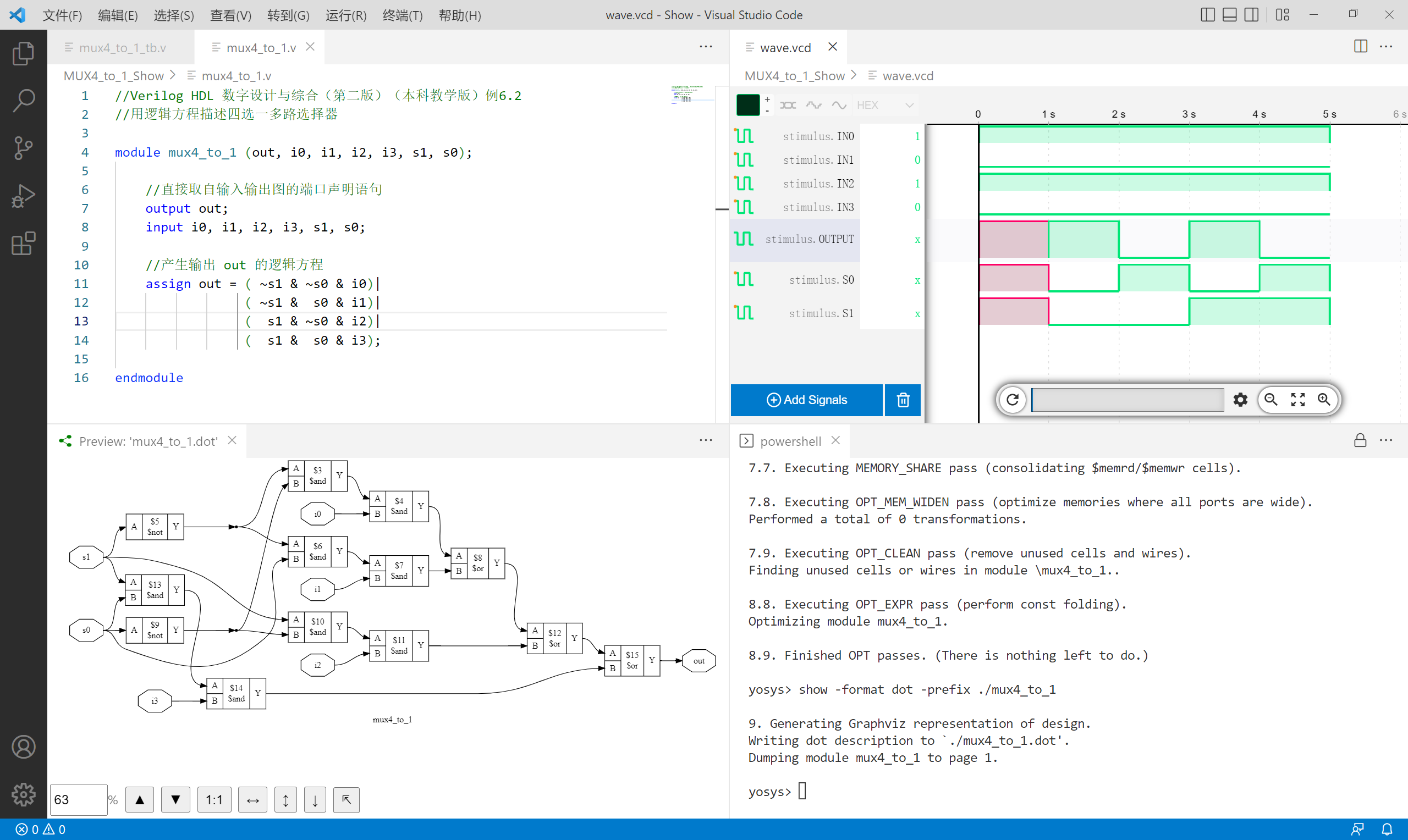

最终结果展示:其中 .dot 文件打开后可以使用快捷键

Ctrl+Shift+v 得到可视化电路图。

注:默认不读入工艺库的话,Yosys 使用自带的工艺库。

Isseus and Solution

这一小节记录一下我初用这个工具链遇到的问题:

Isseus:进行编译和波形测试时,发现VScode上的WaveTrace插件不能正常进行查看,但是使用GTKwave开源查看,我的编译仿真指令如下:

1

2iverilog -o wave -y ./ alu_tb.v alu.v

vvp -n wave -lxt2Solution:使用下面的指令来生成 .vcd 图像:即不要携带

-lxt21

vvp wave

Isseus:Yosys 出现如下报错:

1

ERROR: System task `$display' called with invalid/unsupported format specifier.

Solution:如果出现这个报错,考虑将测试的module放在一个单独的文件中,使yosys操作的对象不包括测试使用的module

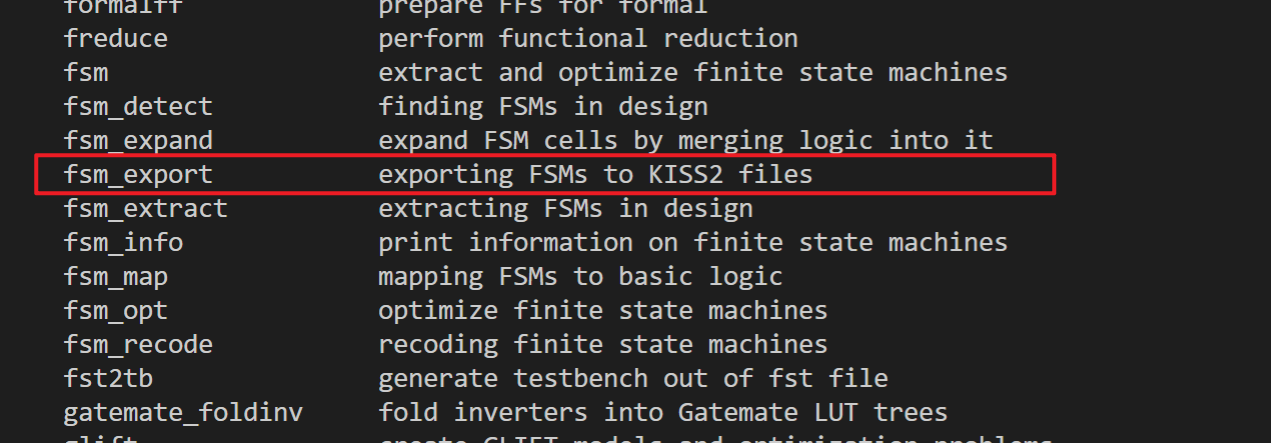

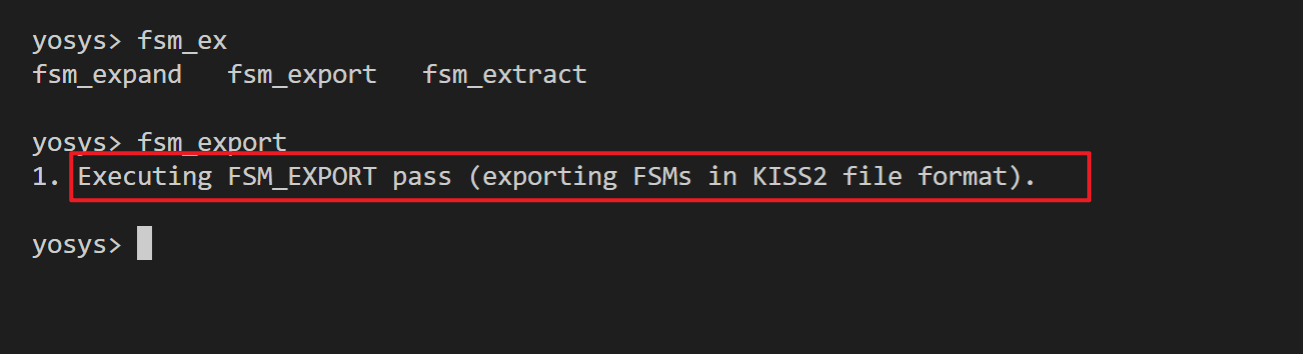

Isseus:==待解决==在 Yosys 命令行中使用 help 指令可以看到 Yosys 中提供指令可以导出有限状态机的图:

即指令

fsm_export,但是在实际操作中使用该指令后打印如下日志:

但是没有 KISS2 文件在操作目录下生成。

Solution:这个问题目前没有被解决,但是这里有两个网页可以提供重要参考

在 Yosys 中使用工艺库

在上面的过程中,我们使用 Yosys 读入 .v

文件,将高层次的描述转化为寄存器传输级描述(RTL)进而得到门级描述,然后在转化中我们都进行了化简和优化。得到的门级描述使用

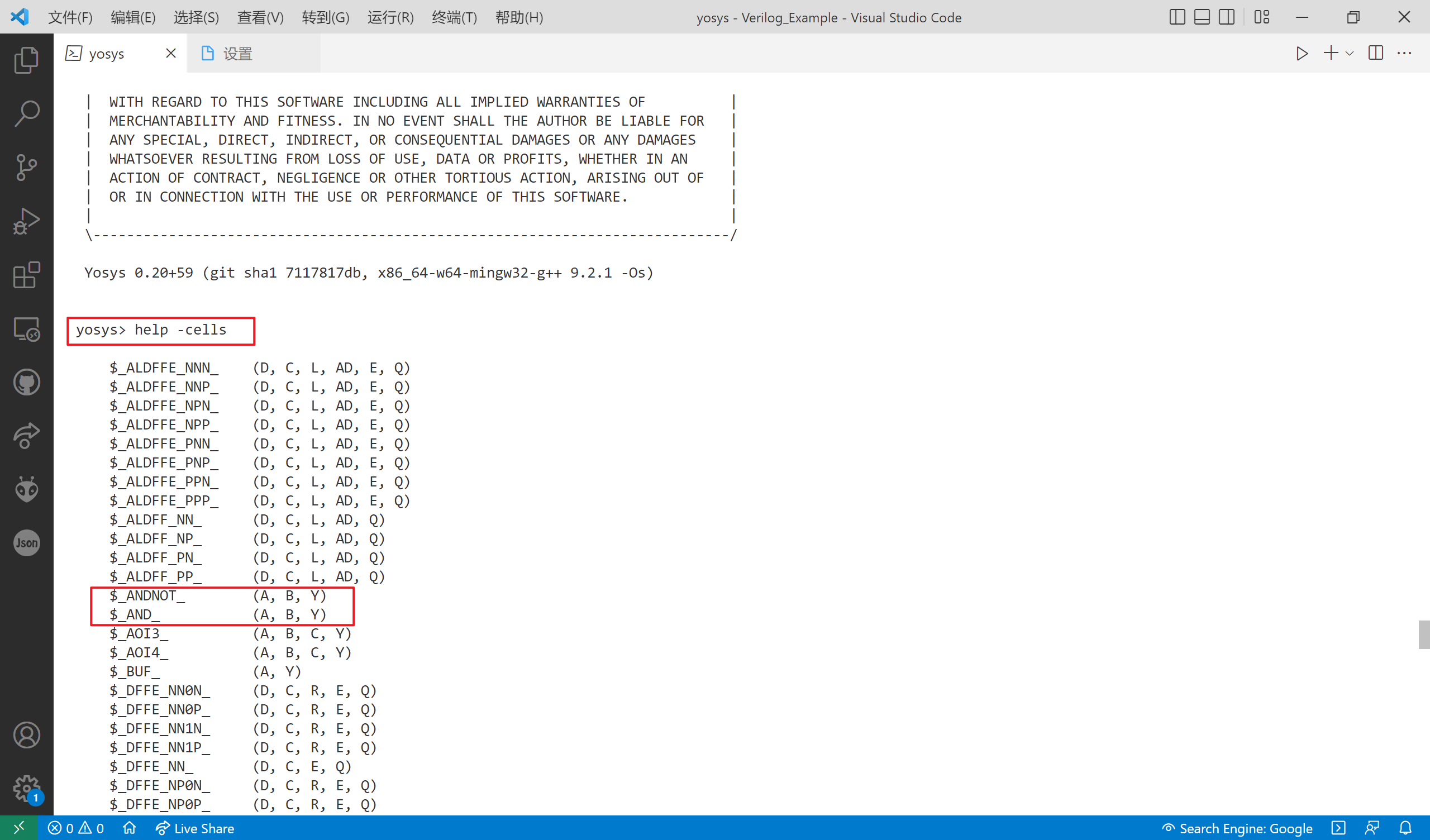

Yosys 自带的单元(cells)进行的描述。我们可以在 Yosys中使用指令

help -cells 来查看 Yosys 默认使用的单元列表:如下图。

我们可以看到 Yosys 中包含有 $_AND_ 或者

$_ANDNOT_

这种单元。首先我们先用默认的单元来综合我们的电路,然后导入新的单元来构建满足新工艺库的电路。

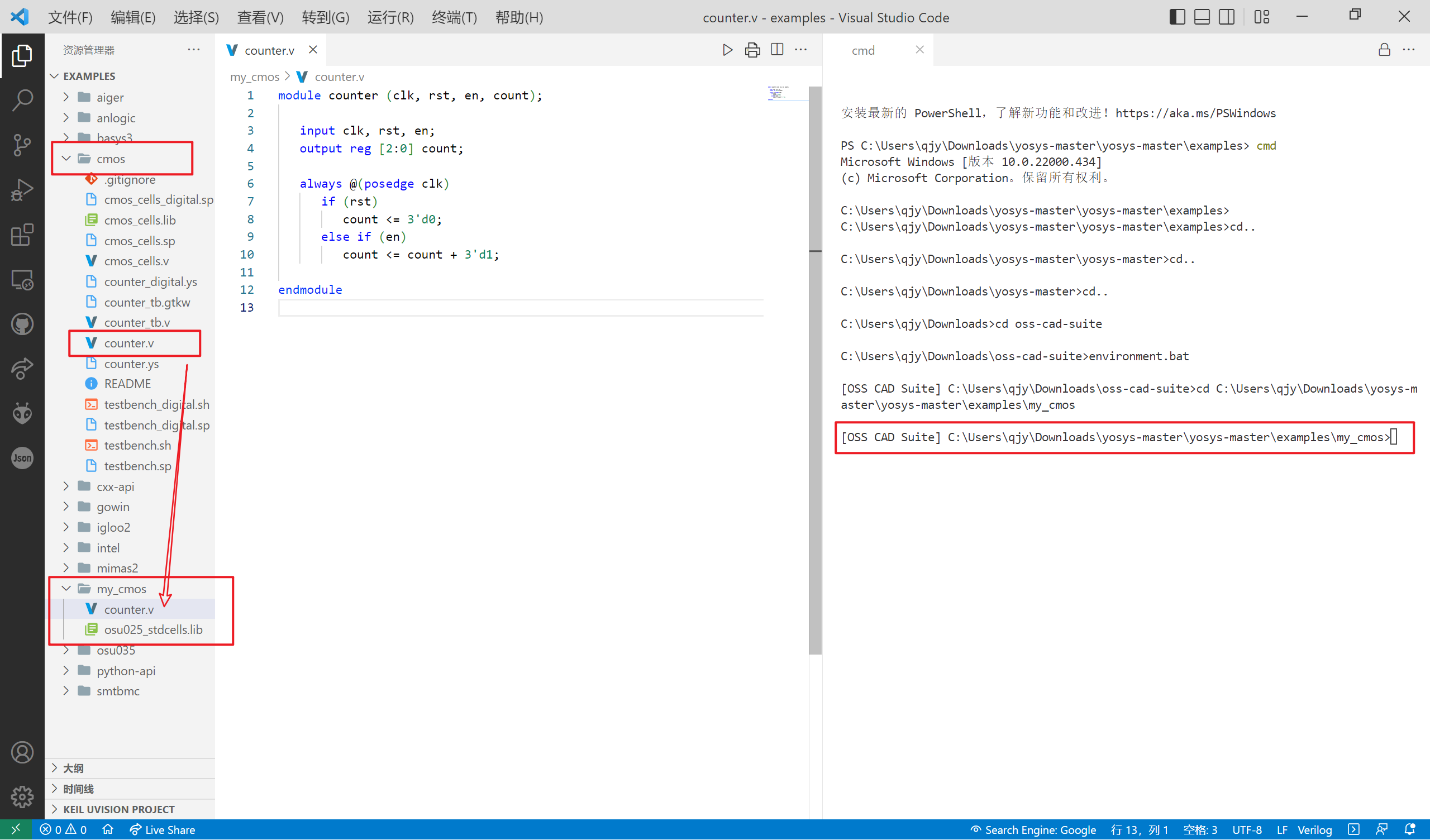

用来演示的 Verilog 文件来自

..\yosys-master\yosys-master\examples\cmos,你可以在这里查看。

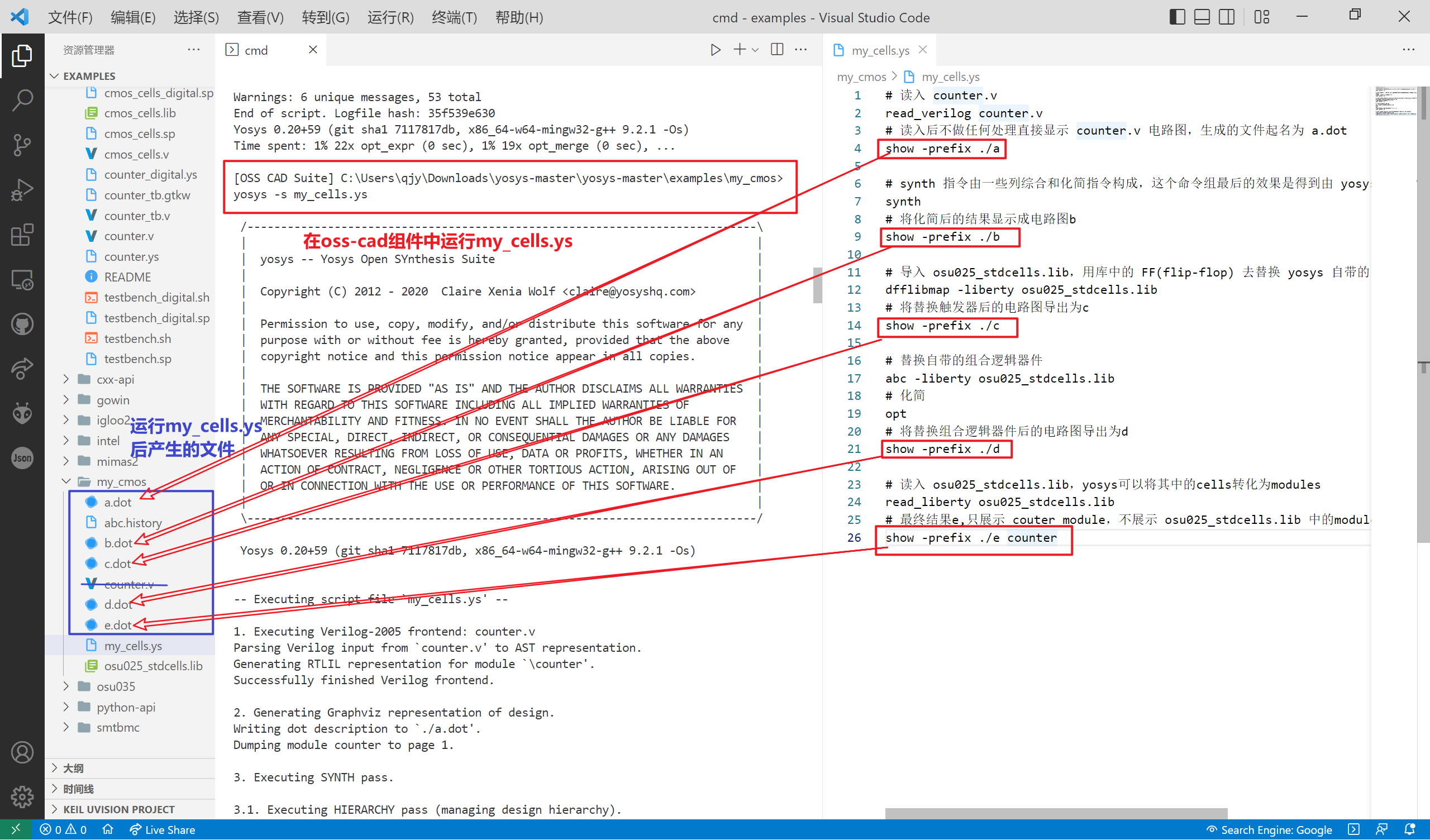

首先我在 ..\yosys-master\yosys-master\examples

目录下创建了一个新的文件夹 my_cmos,然后将

cmos 中的 counter.v 文件移动到

my_cmos 中,然后复制这里的代码到

my_cmos 文件夹中并命名为

osu025_stdcells.lib。最后使用 oss-cad 组件打开

my_cmos 这个文件夹进行后续操作。

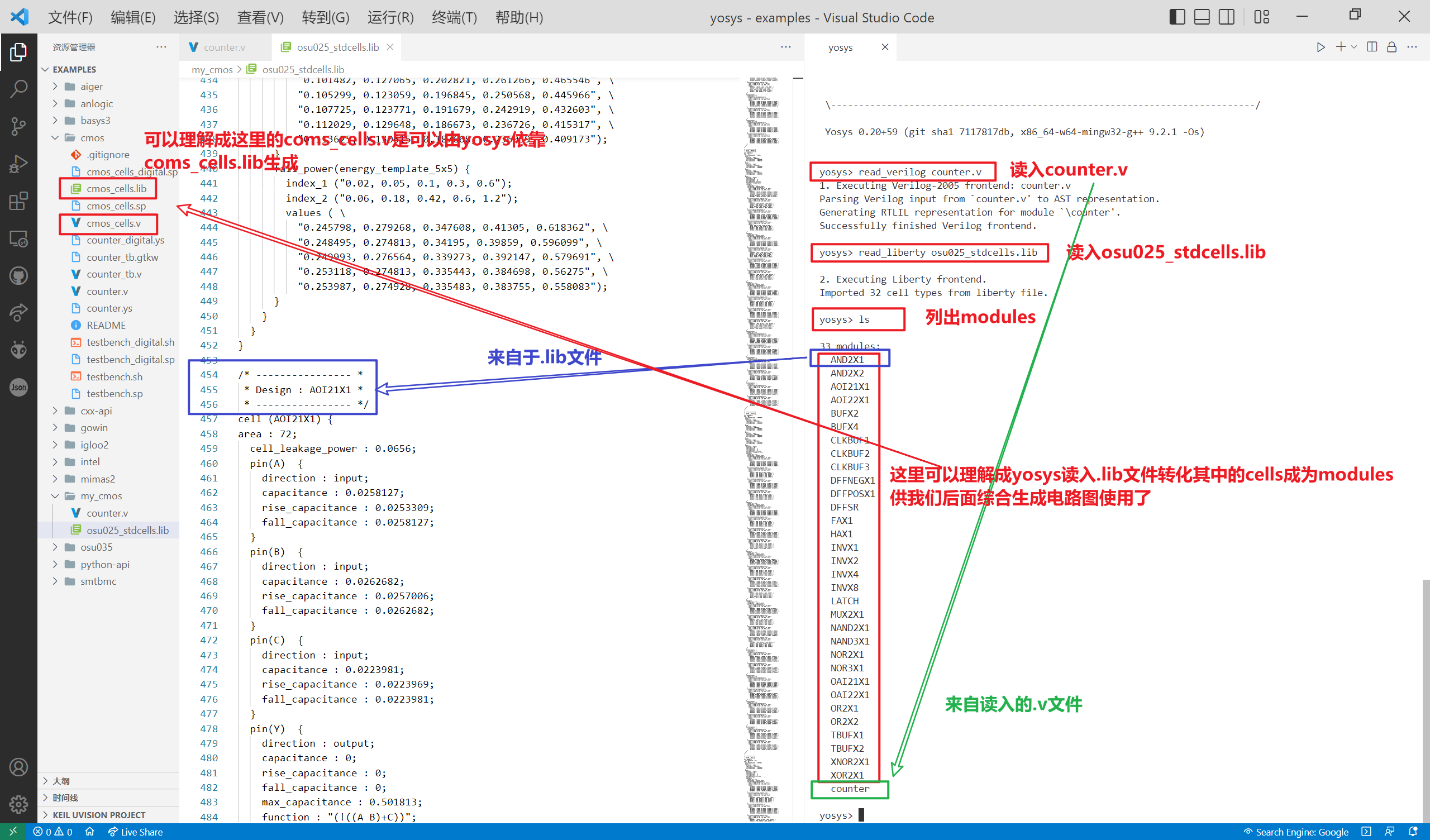

然后进入 Yosys,使用下述指令读入文件到 Yosys:这是我们导入自己的单元库的方法。

1 | read_verilog counter.v |

现在我们使用快捷键 Ctrl+D 退出

Yosys。然后我们来生成电路图展示一下 yosys 对于电路图的处理。同时我们引入

yosys 指令批量处理的方法:

首先将下述指令复制到一个新建文件夹 my_cells.ys

1 | 读入 counter.v |

然后在 oss-cad 组件中使用 yosys -s my_cells.ys

来批量执行指令

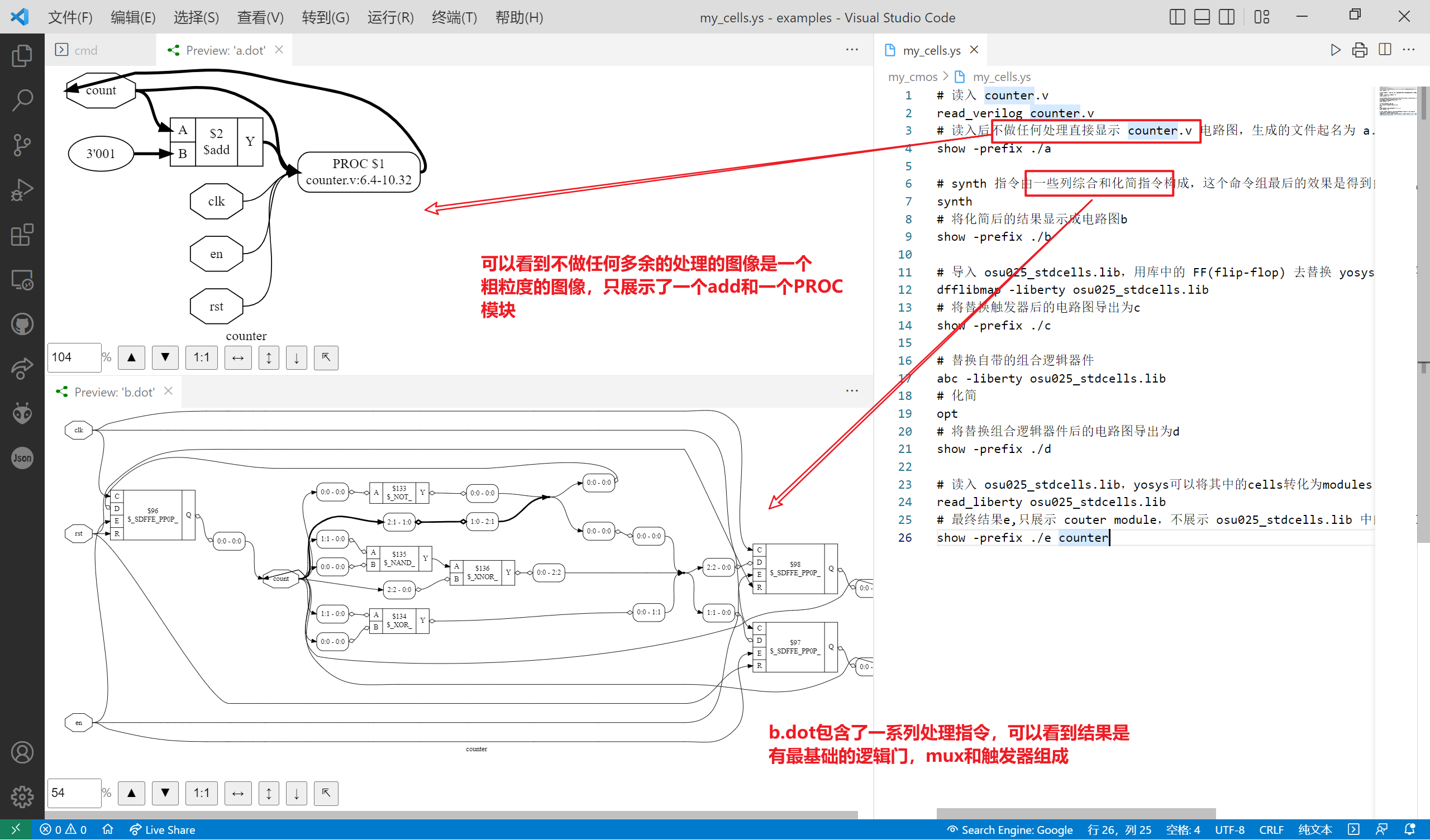

然后打开 .dot 文件观察结果

这两张图重复了使用方法一节中展现的化简过程

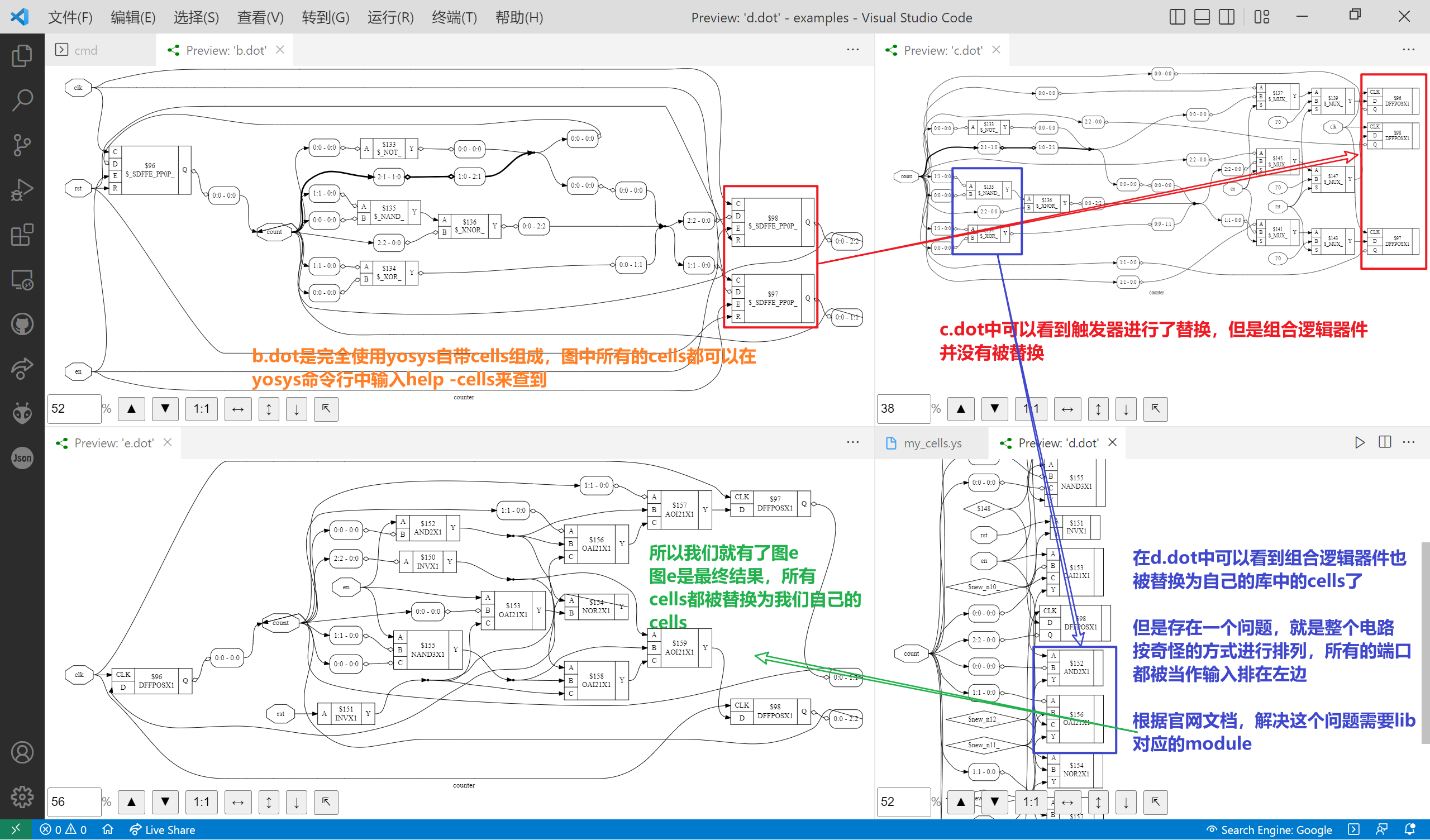

然后我们观察后面几张图

上图为了进行对比,可能图片不是非常清晰,大家可以自己动手做一下然后进行观察。

到此我们就实现了自己的cells库的导入,你可以进一步通过

write_verilog 指令导出综合后的电路图。

进一步的参考

如果想要进一步了解 Yosys 的使用,推荐使用 Yosys AppNote 011、Yosys manual 两篇文章进行学习

如果想要配置 STA 工具,可以参考此工具 OpenTimer